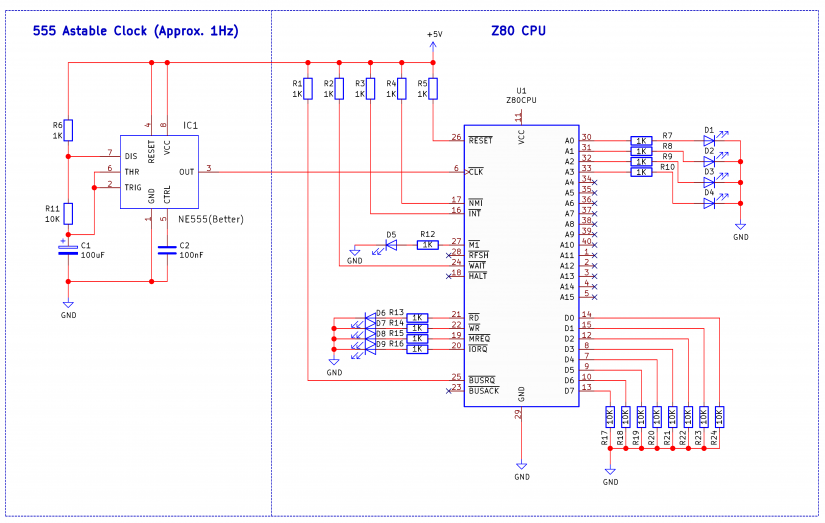

Ranges outside of the bank select 0 for SRAM_A16. In this instance, it means that the A16 should always be set to 1. But the mapping register contents have to be more carefully considered to not cause a conflict with the base page. To generalize, SRAM_A16 could be handled with an extra bit from the Control_Register_1 and an additional multiplexer. With this method the 16KB that was "lost" could be recovered. This simple map is implemented as follows: The range defines where that mapping happens from the Z80 CPU side and how many bits have to be sent out to the SRAM. The window size determines how many of the upper address bits are altered. The size of the SRAM determines how many banks there will be. This is set by the Z80 CPU with an I/O write. The complicating factor here is that the Z80 bank addresses A15 and A14 are replaced by the bits from the bank select register but only when the address is in the banked window. Outside of the banked range the address lines are unchanged. SRAM address lines A16.A14 come out of the mapper but only when the CPU address range is the banked space. The "Banked" area is actually not filled in the "original" SRAM.

Any other CPU address does not get translated but gets directly sent to the SRAM and A16=0. The upper SRAM address, A16 gets set to 1. In the example, if the CPU Address is 0x8000-0xBFFF, the bank switch is selected. This is an illustration of the concept for a 16-bit address bus CPU (like the Z80) with a 16KB bank size and a total of 128 KB of SRAM.

In the simplest scheme, bank switching involves creating a single window in the Z80 memory space and switching in banks of SRAM into the window. The PSoC just sees the memory bank control register as a single 8-bit I/O write which replaces the upper address bits to the SRAM when accesses are in the range of the window. Changing to another bank typically consists of an I/O write from the Z80 to a bank select register. For a typical discussion of where this can go see this EEVBLOG thread which goes on for many pages.Ĭontrol of bank switching can be done with the PSoC and the Z80. Many of them complicate things by trying to replicate a Memory Management unit with multiple banks that can map into multiple locations. There are quite a few Z80 memory bank switching schemes out in the wild.

Bank Switching is used for RAM Disks and possibly other applications where more memory than the CPU address space is desired.

0 kommentar(er)

0 kommentar(er)